DfM

PCB Alignment Tolerance Stack Analysis

Use this text to share information about your brand with your customers. Describe a product, share announcements, or welcome customers to your store.

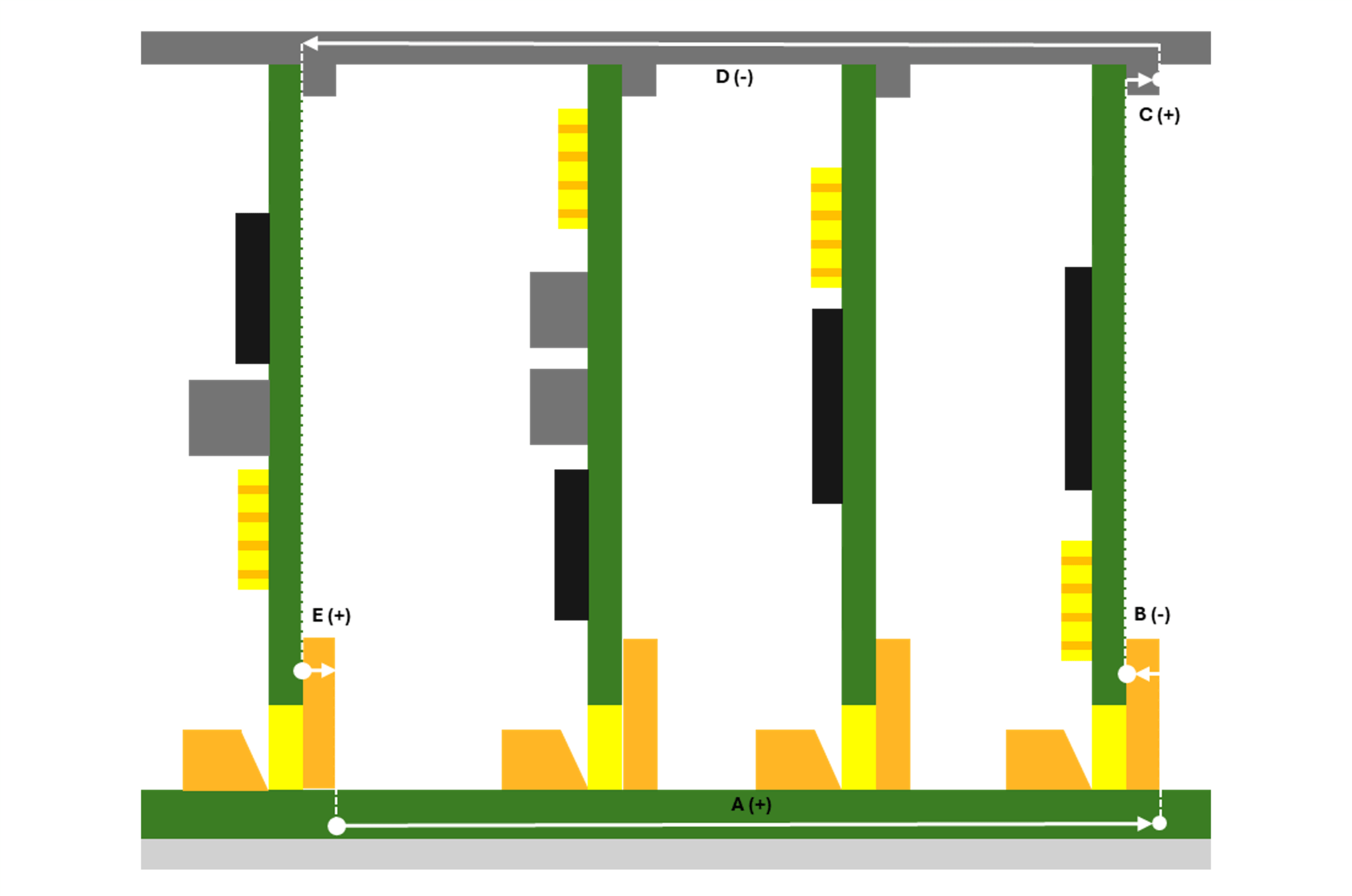

A question was raised as to whether the reconfiguration of electronic cards would allow a PCB within an electronics assembly to be aligned correctly without the need for additional fixtures. The key risk was that tolerance stack-up across the electronic cards and hardware might shift the PCB beyond its allowable position, which would normally be controlled by a dedicated alignment fixture.

To verify the feasibility of reducing the need for additional fixtures, a vector-loop tolerance analysis was performed across the full dimensional stack. This method quantified the cumulative variation arising from the tolerances of each contributing component. The analysis demonstrated that, even at the extremes of tolerance, the resultant PCB position remained within the acceptable alignment limits.

This provided the confidence to formally adopt the revised assembly method. The result was a streamlined build process, reduced dependence on specialist tooling and a faster, more efficient assembly sequence. By addressing tolerance risk analytically rather than reactively, the solution removed uncertainty and supported a controlled, repeatable manufacturing outcome.

This project highlights how robust tolerance modelling can enable practical process improvements and deliver measurable benefit with low intervention.